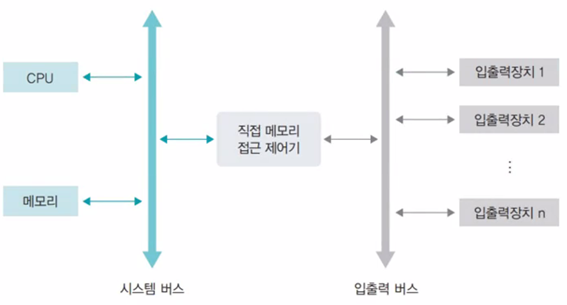

폰 노이만 구조

CPU, 메모리, 저장장치,입출력장치가 버스로 연결되어있는 구조

CPU 클럭 주파수

클럭: CPU 연산

주파수: 초당 클럭 수

hz: 주파수 단위, 컴퓨터의 작업 속도를 타나내는 단위

Ex) 3.4 Ghz = CPU가 1초에 약 34억번의 연산을 함

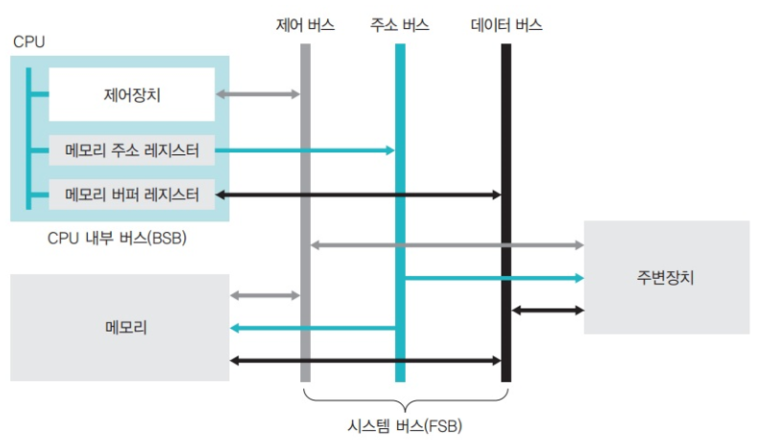

버스

시스템 버스(FSB): 메모리와 주변 장치를 연결하는 버스

BSB: CPU 내부 장치를 연결하는 버스

-> CPU는 BSB로 작동, 메모리는 FSB로 작동 -> 두 버스의 속도 차이로 인하여 작업이 지연될 수 있음 -> Cache로 해결

CPU의 구성

산술논리 연산장치(ALU) – 논리 연산 수행

제어장치 – CPU에서 작업을 지시하는 부분

레지스터 – CPU 내에서 데이터를 임의로 보관하는 곳

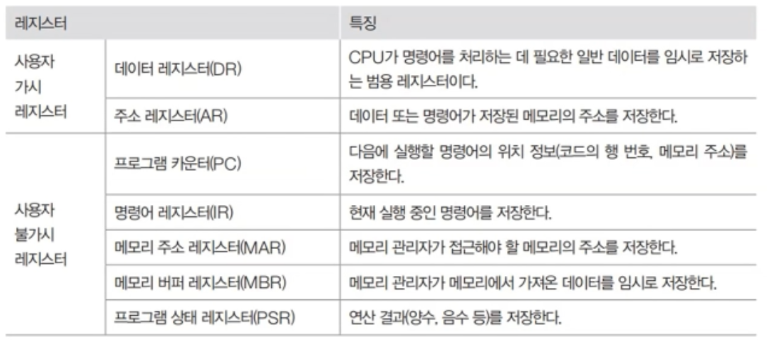

주요 레지스터의 종류와 특징

버스(FSB)의 종류

제어 버스 – CPU 제어장치와 연결된 버스

주소 버스 – 메모리 주소 레지스터와 연결된 버스

데이터 버스 – 메모리 버퍼 레지스터와 연결된 버스

버스 대역폭: 한 번에 전달할 수 있는 데이터의 최대 크기

메모리 보호 방법: 경계, 한계 레지스터를 이용한다.

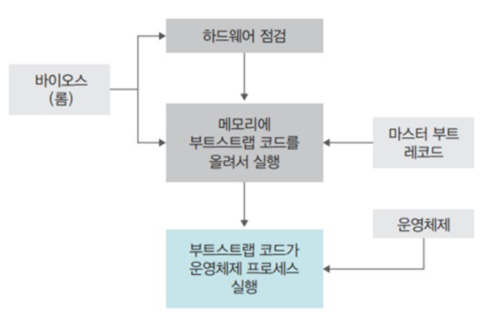

부팅

컴퓨터를 켰을 때 운영체제를 메모리에 올리는 과정

- ROM이 갖고 있는 바이오스를 실행한다.

- 바이오스는 CPU, 메모리, 하드디스크, 키보드, 마우스와 같은 주요 하드웨어가 제대로 작동하는지 확인한다.

- 부트 스트랩 코드(운영체제를 실행하기 위한코드)를 메모리에 올리고 실행한다. 부트 스트랩 코드는 보통 하드디스크의 첫 번째 섹터에 위치한다.

- 부트스트랩 코드가 운영체제를 실행한다.

버퍼, 스풀, 캐시

버퍼

속도에 차이가 있는 두 장치 사이에서 그 차이를 완화하는 역할을 하는 장치

(주기억 장치를 버퍼로 사용한다)

스풀

CPU와 입출력장치 사이의 속도 차이를 완화하기 위해 고안된 소프트웨어적인 버퍼

(디스크를 버퍼로 사용한다)

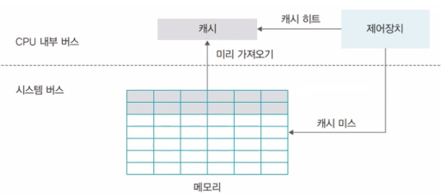

캐시

메모리와 CPU간의 속도 차이를 완화히기 위해 메모리의 데이터를 미리 가져와 저장해두는 임시 장소

(CPU는 캐시를 방문해서 원하는 데이터가 있는지 없는지 보고 없으면 메모리로 감)

(메인 메모리는 DRAM, 캐시는 SRAM 사용)

캐시의 구조

캐시 히트: 캐시에서 원하는 데이터를 찾고 바로 사용

캐시 미스: 원하는 데이터가 캐시에 없으면 메모리로 가서 데이터를 찾음

캐시 적중률: 캐시 히트가 되는 비율 (일반적인 컴퓨터의 캐시 적중률은 약 90%)

-> 캐시에 적중되는 횟수/전체 접근된 횟수

(문제) 캐시와 주기억장치로 구성된 컴퓨터에서 주기억장치의 접근 시간이 200ns, 캐시 적중률이 0.9, 평균 접근 시간이 30ns일 때 캐시 메모리의 접근 시간은?

정답: 10

풀이: 캐시 메모리의 접근 시간을 x라고 했을 때, 0.9x+0.1(x+200)=30이 된다. 왜냐하면 90%는 캐시에 접근하고 10%는 캐시에 접근했다가 주기억 장치에 접근하기 때문이다. [적중률 x 캐시 접근 시간]과 [(1-적중률) x (캐시 접근 및 메모리 접근 시간)]을 합치면 평균 접근 시간이 나온다. 캐시 접근 시간(x)는 위 방정식을 풀면 나온다.

(문제) 주기억 장치의 접근 시간이 700ns이고 캐시의 접근 시간이 100ns이며 평균 접근 시간이 170ns일 때 적중률은?

정답: 90%

풀이: 적중률을 x라고 했을 때, x(100)+(1-x)(100+700)=170이 된다. 왜냐하면 x%는 캐시에 접근하고 (1-x)%는 캐시에 접근했다가 주기억 장치에 접근하기 때문이다. [적중률 x 캐시 접근 시간]과 [(1-적중률) x (캐시 접근 및 메모리 접근 시간)]을 합치면 평균 접근 시간이 나온다. 적중률(x)은 위 방정식을 풀면 나온다.

- 캐시 용량이 커질수록 히트율은 높아지지만 비용이 증가

- CPU 또는 메인보드의 크기도 고려해야 됨

즉시 쓰기(write-through): 캐시에 있는 데이터가 변경되면 이를 즉시 메모리에 반영하는 방식

- 메모리와의 빈번한 데이터 전송으로 인해 성능이 느려짐

- 메모리의 최신 값이 항상 유지되기 때문에 급작스러운 정전에도 데이터를 잃어버리지 않음

지연 쓰기(write-back): 캐시에 있는 데이터가 변경되면 내용을 모아서 주기적으로 반영하는 방식

- 메모리와의 데이터 전송 횟수가 줄어들어 시스템의 성능을 향상할 수 있음

- 메모리와 캐시된 데이터 사이의 불일치가 발생할 수도 있음

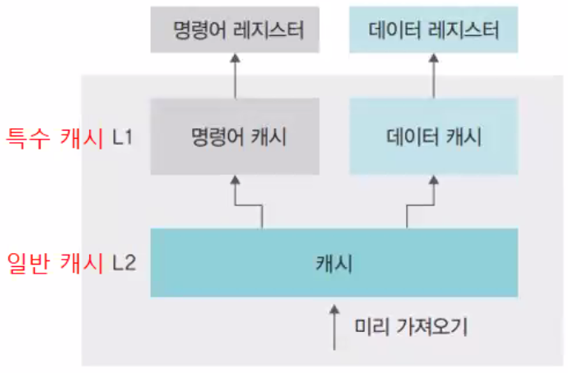

특수 캐시 L1: CPU 레지스터에 직접 연결됨

일반 캐시 L2: 메모리와 연결됨

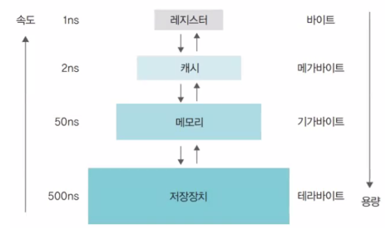

저장 장치의 계층 구조

속도가 빠르고 값이 비싼 저장 장치를 CPU 가까운 쪽에 두고, 값이 싸고 용량이 큰 저장 장치를 반대쪽에 배치하여 적당한 가격으로 빠른 속도와 큰 용량을 동시에 얻는 방법

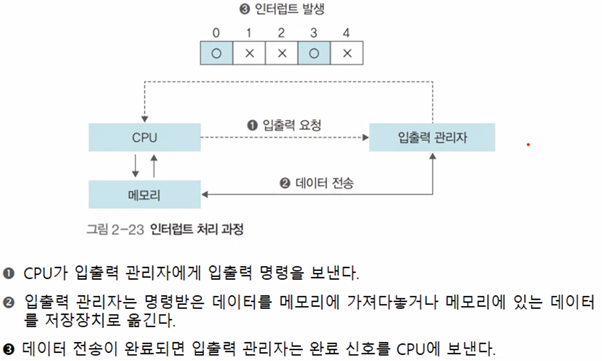

인터럽트

폴링 방식: CPU가 직접 입/출력 장치에서 데이터를 가져오거나 내보내는 방식

인터럽트 방식: 입출력 관리자가 대신 입출력을 해주는 방식

입/출력 예시: 저장 장치에서 버퍼로 갖고 오는 것 / 버퍼에 있는 내용을 쓰는 것

(인터럽트 설명에는 저장 장치도 입출력 장치로 취급하는 것 같음)

인터럽트: 입출력 관리자가 CPU에 보내는 완료 신호

인터럽트 번호: 많은 주변장치 중 어떤 것의 작업이 끝났는지를 CPU에 알려주기 위해 사용하는 번호

(윈도우에서는 IRQ)

인터럽트 벡터: 여러 개의 입출력 작업을 한 번에 처리하기 위해 여러 개의 인터럽트를 하나의 배열로 만든 것

직접 메모리 접근 (DMA)

입출력 관리자가 CPU의 허락없이 메모리에 접근할 수 있는 권한

사이클 훔치기: CPU와 직접 메모리 접근이 동시에 메모리에 접근하면 보통 CPU가 메모리 사용 권한을 양보

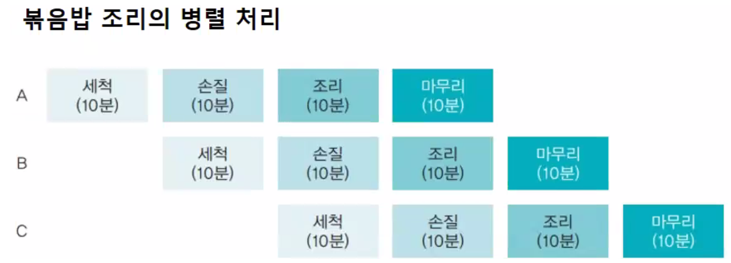

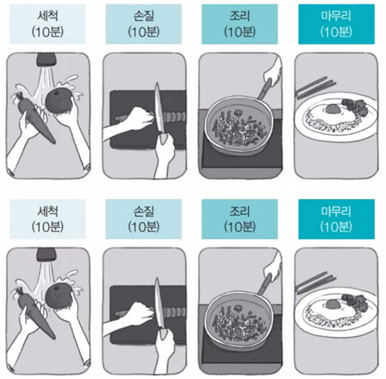

병렬 처리

동시에 여러 개의 명령을 처리하여 작업의 능률을 올리는 방식

Ex) 볶음밥 세 개를 병렬 처리로 만들기 -> 60분만에 처리

병렬처리 기법

슈퍼스칼라 기법

듀얼코어 CPU를 이용해 2개의 작업을 동시에 처리하는 방식

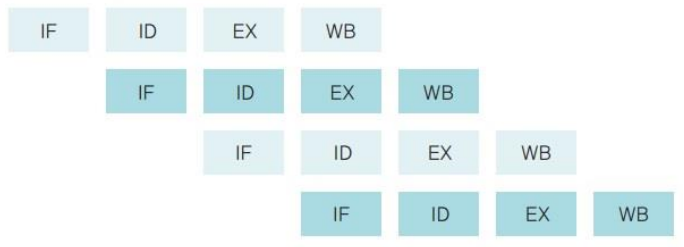

파이프라인 기법

CPU의 사용을 극대화하기 위해 명령을 겹쳐서 실행하는 방법

병렬처리 주의점

1. 상호 의존성이 없어야 병렬 처리가 가능

각 명령이 서로 독립적이고 앞의 결과가 뒤의 명령에 영향을 미치지 않아야 함

2. 각 단계의 시간을 일정하게 맞춰야 병렬 처리가 원만하게 이루어짐

Ex) 세척을 끝냈으나 다음 손질까지 기다리려면 5분을 기다려야 됨

전체 작업 시간을 몇 단계로 나눌지 잘 따져보아야 함

CPU에서 명령어가 실행되는 과정

- 명령어 패치: 다음에 실행할 명령어를 명령어 레지스터에 저장

- 명령어 해석: 명령어 해석

- 실행: 해석한 결과를 토대로 명령어 실행

- 쓰기: 실행된 결과를 메모리에 저장

파이프라인 기법의 위험성

데이터 위험: 데이터의 의존성 때문에 발생하는 문제

제어 위험: 프로그램 카운터 값을 갑자기 변화시켜 발생하는 위험

구조 위험: 서로 다른 명령어가 같은 자원에 접근하려 할 때 발생하는 문제

슈퍼 파이프라인 기법

파이프라인의 각 단계를 세분하여 한 클록 내에 여러 명령어를 처리

한 클록 내에 여러 명령어를 실행하면 다음 명령어가 빠른 시간 안에 시작될 수 있어 병렬 처리 능력이 높아짐

슈퍼파이프라인 슈퍼스칼라 기법

슈퍼파이프라인 기법을 여러 개의 코어에서 동시에 수행하는 방식

CPU가 병렬처리를 지원하지 않을 때!

VLIW 기법: 소프트웨어적으로 병렬처리를 하는 방법

(기존 병렬 처리 기법들에 비해 동시에 처리하는 명령어의 개수가 적음)